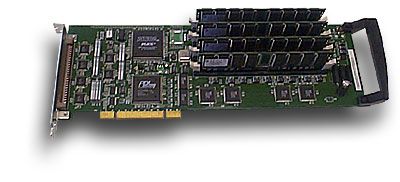

200MHz高速數(shù)字輸入\輸出(I/O)卡

生產(chǎn)廠商: 迪陽公司代理

產(chǎn)品型號: PCI-DMI32

產(chǎn)品簡介: The DMI will transfer up to 4GB of unique data continuously at up to 50 Mhz Provides for data I/O via the cable at up to 200 Mbytes per second (LVDS differential I/O) Can transfer data indefinitely without host intervention

產(chǎn)品簡介: The DMI will transfer up to 4GB of unique data continuously at up to 50 Mhz Provides for data I/O via the cable at up to 200 Mbytes per second (LVDS differential I/O) Can transfer data indefinitely without host intervention

特性:

| Description | ||

|

|||

北京迪陽世紀(jì)科技有限責(zé)任公司 版權(quán)所有 ? 2008 - 2018 著作權(quán)聲明

010-62156134 62169728 13301007825 節(jié)假日:13901042484 微信號:sun62169728

地址:北京市西城阜外百萬莊扣鐘北里7號公寓

E_mail:[email protected] 傳真: 010-68328400

京ICP備17023194號-1 公備110108007750

010-62156134 62169728 13301007825 節(jié)假日:13901042484 微信號:sun62169728

地址:北京市西城阜外百萬莊扣鐘北里7號公寓

E_mail:[email protected] 傳真: 010-68328400

京ICP備17023194號-1 公備110108007750

售價:¥0

售價:¥0